- #Cadence vlsi design tool update#

- #Cadence vlsi design tool software#

- #Cadence vlsi design tool code#

- #Cadence vlsi design tool license#

- #Cadence vlsi design tool simulator#

I have listed some of the popular VLSI EDA tools. Related Read: Free Download Electrical CAD (ECAD) Softwares Having a basic coding knowledge of C/C++, embedded C programming, Matlab/Simulink and scripting languages (like TCL, Perl) will be useful for learning VLSI designing. HDL consists of different languages such as Verilog, VHDL, and SystemVerilog. Which Programming Language is Used in VLSI?įor VSLI design, hardware description language (HDL) is used.

#Cadence vlsi design tool software#

These expensive in cost.įor learning purposes, you can use open-source software tools like Electric, Alliance, Glade. Synthesized netlist (from synthesis tool : Design compiler or RTL. The files required for this experiment is: a. In this experiment we perform pre-layout STA. STA can be performed on both pre-layout and post-layout netlist. The VLSI Fundamentals: A Practical Approach Education Kit using Cadence tools is available for download from the Cadence Academic Network webpage after completing registration. In this experiment, we are performing Static Timing Analysis using Cadence Tempus. 2- Then the output of the modeling and verification, which is the test vectors, is passed to RTL team to design the hardware.

#Cadence vlsi design tool license#

To use these software’s you have to purchase the license as they are not open source. At Cadence, we offered our support to optimize the kit with the latest Cadence digital implementation software: Genus Synthesis Solution and Innovus Implementation System. for the front end : 1- It starts from system-level description and verification, like extracting the architecture from an IEEE standard and modeling the system using C/C++/SystemC or Matlab. In the industrial environment, Cadence virtuoso, Synopsys, and Mentor Graphics are mostly used. And some are licensed based for which you have to pay. Some of these tools are open-source and available for free. List of Electronic Design Automation (EDA) tools:

#Cadence vlsi design tool update#

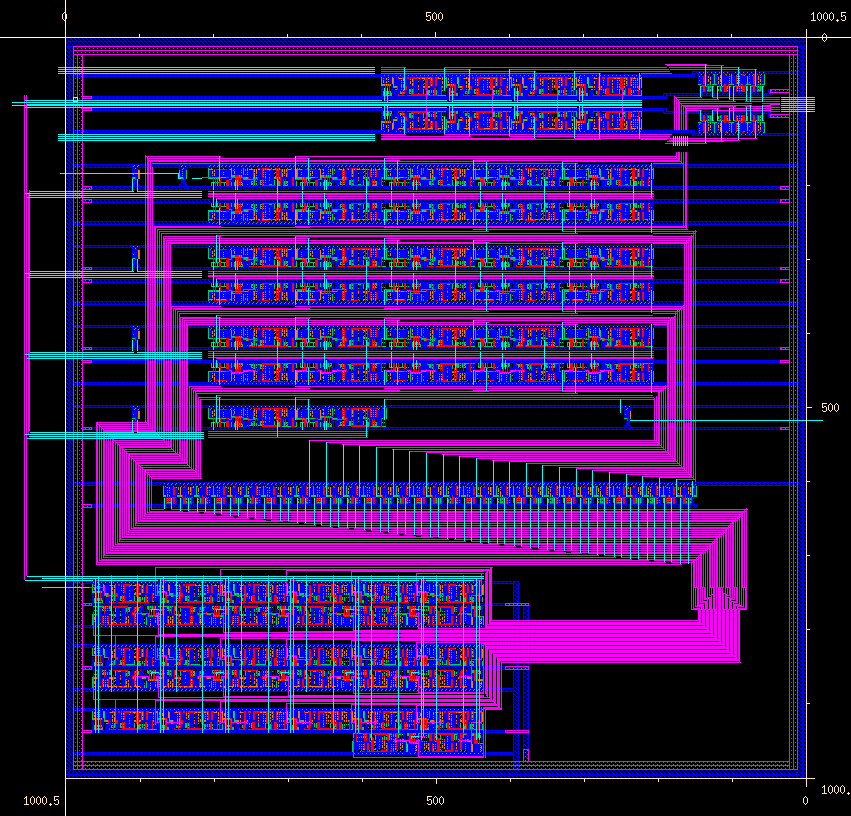

To stay up to date when selected product base and update releases are available, Cadence Online Support users may set up their Software Update Preferences. If you are from India, there are many top institutes that offer VLSI course. Cadence ® software is available through electronic distribution to customers with a current maintenance agreement and Cadence Online Support, or eDA-on-Tap website accounts. There are multiple EDA tools available in the market. Top 10 online Cadence Virtuoso teachers & Cadence Virtuoso home teachers. It uses multiple features like logical design, circuit schematic design, layout generation, design simulation and may more features for VSLI design. EDA tools help to create multiple types of electronic circuits like an integrated circuit (IC), printed circuit board (PCB) and system on chip (SoC). It is a software tool used to design the electronic circuit. EDA is also known as Electronic Computer-Aided Design (ECAD).

#Cadence vlsi design tool code#

What are the EDA Tools for VLSI design? Write Verilog Code for the following circuits and their Test Bench for verification, observe the waveform and synthesize the code with the technological library.the final output is the layout itself, which goes to the Fab House as a file called GDSII. For the backend people, they take the netlist with the timing inputs, then start layouting the chip in many steps. Simply, u get the netlist out of this process (without more details), then pass it to the backend people. ECE 6130/4130 (Advanced VLSI Systems): The Virtuoso schematic/layout editors and Diva/Calibre DRC/LVS/Extraction tools are used in this course to teach students advances concepts of digital system design using the NCSU Design Kit.

Most of the time, people use Design Compiler (by Synopsis) and some others use Leonardo (By Mentor). The Cadence tools in this course introduces students to the basic VLSI design skills. or any other RTL simulator/wave viewer from Cadence or Synopsis as mentioned before.ģ- After the design is verified on the RTL level, it goes for Synthesis and Netlist generation.

#Cadence vlsi design tool simulator#

This designed hardware has be simulated using an HDL simulator like Mentor Graphics' Modelsim (commonly used). 1- It starts from system-level description and verification, like extracting the architecture from an IEEE standard and modeling the system using C/C++/SystemC or Matlab.Ģ- Then the output of the modeling and verification, which is the test vectors, is passed to RTL team to design the hardware using any common HDL language like VHDL or Verilog.

0 kommentar(er)

0 kommentar(er)